euresys产品

Euresys / Sensor以图像提供了一组IP核心和开发框架,用于使用USB3视觉界面构建基于FPGA的产品。由于USB3愿景的速度,发件人和接收器需要快速的FPGA的实现嵌入式USB核心。USB3视觉核心兼容Xilinx 7系列设备(更高版本)和英特尔/ Altera Cyclone V器件(更高版本)。

USB3 Vision IP核心FPGA,一目了然兼容Xilinx 7系列(和较新的)和英特尔/ Altera Cyclone V器件(以及更新)紧凑,可通过工作参考设计提供可定制的

来自euresys的其他产品

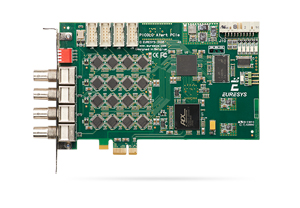

Picolo警报PCIe.

4x BNC连接器上的支架上,可扩展为16,三[1203] VEB模块(单独出售)PCIe X1总线十六分享视频解码器,每秒100/120图像(每秒200/240字段)从4个摄像机的实时采集,快速切换多达16个摄像机可独立可编程帧速率和每个视频输入的采集参数